関連記事

東芝・キヤノン連合、次世代「BiCS FLASH」の微細化技術 サムスンに対抗

サムスンに対抗するフラッシュメモリの設計・生産技術は、粛々と開発されている模様。東芝とキヤノンは、1テラバイトの大容量化も実現した。

【こちらも】東芝、3次元フラッシュメモリー生産拡大に1800億円投資

東芝は11日、TSV技術を用いて1テラバイトのフラッシュメモリを開発したと発表。また、キヤノンは20日、ナノインプリント技術を用いた半導体製造装置を東芝に納入と発表した。この2つの発表は、東芝経営再建のニュースの陰で、大きく報道されることはなかった。3次元構造のフラッシュメモリ技術で先行するサムスン、追いかける東芝。フラッシュメモリの市場競争力の源泉である設計・生産技術の報道は、平時ならば大々的に取り上げられる話題であって然るべきである。

●フラッシュメモリの大容量化は、3次元構造と微細化の複合技術

今回報道された技術は、3次元構造に関する設計製造技術(東芝)と露光に関する製造技術(キヤノン)であり、どちらも世界初という。

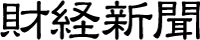

3次元化技術は、大容量化要求に対して、微細化の限界を緩和する技術であり、その構造の決め方にノウハウや技術が集約される。セルと呼ばれる記憶回路を、横置きから、縦積みに積層すると、チップの記憶容量は増す。例えば、平屋建てと高層マンションとの違いと同じである(図1参照)。加えて、完成したチップも縦積みに積層するThrough Silicon Via(TSV)技術を組み合わせる。TSVは、チップ内部を垂直に貫通する電極を用いて、複数チップをパッケージ内で積層する技術である。

露光技術は、光で回路を焼き付ける技術で、光の波長を短くして、微細な回路を構成する。課題は、光の波長よりも、1/10倍も微細な回路を焼き付けることである。そのため、露光技術の高度化か、新たな技術開発かは、技術・経営判断である。キヤノンは、新たなナノインプリント技術(図2参照)を東芝と共同研究し、今回の納入となる。なお、露光装置メーカートップのASMLは、露光技術の高度化で先行し、サムスンに納入している。

●フラッシュメモリ(東芝「BiCS FLASH」)のテクノロジー

市場競争力の源泉は、ビット当たりの単価と付加価値であろう。東芝の一連の発表から見えてくる最初の技術は、積層化である。セル情報の多値化、チップ内の積層化、そしてパッケージ内の積層化で、微細限界下での大容量化を狙う。今回、3ビット/セル、チップ内48層積層、パッケージ内16段積層を用いて、1テラバイトの大容量化を実現したという。なお、この積層化の構造からは、高速化や低消費電力化の付帯効果も得られている。

第2の技術は、ECCと呼ばれるエラー訂正能力と書き込み制御であろう。エラー訂正なしでは、ほとんどのフラッシュメモリは不良品となってしまう。種々のエラー訂正アルゴリズムの開発実績と経験は侮れない。また、フラッシュメモリは書き込み回数制限がある。この制限緩和のために、均等な書き込みになるよう制御する。

第3の技術は、露光装置に代わるナノインプリントであろう。マスク(型)をウエハー上のレジスト(樹脂)に、スタンプのように直接押し付けることで、マスクの回路パターンを忠実に転写するという。優位な点は、この製造装置の価格が露光装置に比べて安価であることのようだ。ナノインプリントの処理能力や歩留りも露光装置に比べて優位であれば、市場競争力は一気に増すであろう。(記事:小池豊・記事一覧を見る)

スポンサードリンク